(19)

(12)

# (11) **EP 2 624 456 A2**

**EUROPEAN PATENT APPLICATION**

(43) Date of publication:07.08.2013 Bulletin 2013/32

Europäisches Patentamt European Patent Office Office européen des brevets

- (21) Application number: 13153399.4

- (22) Date of filing: 31.01.2013

- (84) Designated Contracting States: AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR Designated Extension States: BA ME

- (30) Priority: **31.01.2012** PL 39795212

- (71) Applicant: AKADEMIA GORNICZO-HUTNICZA im. Stanislawa Staszica 30-059 Krakow (PL)

#### (51) Int Cl.: *H03M 1/12* <sup>(2006.01)</sup>

H03M 1/46 (2006.01)

- (72) Inventors:

Koscielnik, Dariusz 31-431 Krakow (PL)

Miskowicz, Marek 31-636 Krakow (PL)

- (74) Representative: Kacperski, Andrzej Kancelaria Prawno-Patentowa ul. Kupa 3/9 31-057 Krakow (PL)

# (54) Method and apparatus for clockless conversion of instantaneous voltage value to digital word

(57)Method consists in accumulation of electric charge in the sampling capacitor (C<sub>n</sub>) by parallel connection of the sampling capacitor (Cn) to the source of converted voltage (U<sub>IN</sub>) and in realization of the process of charge redistribution in the array of redistribution (A) by changing states of signals from relevant control outputs and in assignment of relevant values to bits in the digital word by means of the control module (CM). Method is characterized in that after detection of the beginning of the next trigger signal  $(P_{x+1})$ , the charge is accumulated in the additional sampling capacitor (C<sub>nA</sub>), and then the process of charge redistribution is realized and relevant values are assigned to bits of the digital word. When the beginning of the subsequent trigger signal (P<sub>x+2</sub>) is detected, the next cycle begins and electric charge is accumulated in the sampling capacitor ( $\mathrm{C}_{\mathrm{n}}$ ) again.

Apparatus comprises the array of redistribution (A), the section of the sampling capacitor (An), the control module (CM), two comparators (K1 and K2) and the current source (J) connected in a known way. Apparatus is characterized in that the additional sampling capacitor ( $C_{nA}$ ) and top plate change-over switches ( $S_{Tn}$ ,  $S_{TnA}$ .  $S_{Bn}$ ,  $S_{BnA}$ ) are connected in the section of the sampling capacitor ( $C_{n-1A}$ ) having the highest capacitance value in the array of redistribution and the bottom plate change-over switches ( $S_{Tn-1}$ ,  $S_{Tn-1A}$ ,  $S_{Bn-1}$ ,  $S_{Bn-1A}$ ) are connected to the capacitor ( $C_{n-1}$ ) having the highest capacitance value in the array of redistribution in a similar way as to the sampling capacitor ( $C_{n-1}$ ).

Printed by Jouve, 75001 PARIS (FR)

#### Description

**[0001]** The subject of this invention is a method and an apparatus for clockless conversion of an instantaneous voltage value to a digital word that can be applied in monitoring and control systems.

- <sup>5</sup> **[0002]** The method for the conversion of an instantaneous voltage value to a digital word known from WO/2011/152745 consists in mapping the converted voltage value to a portion of electric charge proportional to this converted voltage value. A given portion of charge is accumulated in the sampling capacitor by connecting this sampling capacitor in parallel to the source of the converted voltage during the active state of the signal on the trigger input. After detecting the end of the active state of the signal on the trigger input, the accumulated electric charge is submitted to the process

- of redistribution by deploying the charge in the array of capacitors while a capacitance value of each capacitor of a given index is twice as high as a capacitance value of a capacitor of the previous index. During the process of redistribution, the accumulated electric charge is deployed in the capacitors in the array in a way that the obtained voltage equals zero or equals the reference voltage on each capacitor or on each capacitor with the possible exception of one of capacitors. The course of the process of redistribution is controlled by means of the control module on the basis of output signals

- of the first and of the second comparator. Electric charge is transferred between capacitors during the process of its redistribution by the use of the current source. By means of the control module, the value one is assigned to these bits in the digital word that correspond to capacitors on which voltage equal to the reference voltage value has been obtained and the value zero is assigned to the other bits in the digital word. In one of variants of this solution, electric charge is accumulated simultaneously in the sampling capacitor and in the capacitor of the highest capacitance value in the array of capacitors which is connected to the sampling capacitor in parallel.

- of capacitors which is connected to the sampling capacitor in parallel. [0003] The apparatus the conversion of an instantaneous voltage value to a digital word is also known from the description of Polish patent application P-391420. This apparatus comprises the array of capacitors whose control inputs are connected to the set of control outputs of the control module. The control module is equipped with the digital output, the complete conversion signal output, the trigger input and two control inputs. The first control input of the control module

- <sup>25</sup> is connected to the output of the first comparator whose inputs are connected to one pair of outputs of the array of capacitors. The other control input of the control module is connected to the output of the second comparator whose inputs are connected to the other pair of outputs of the array. Furthermore, the source of converted voltage value, the source of auxiliary voltage together with the source of the reference voltage, the sampling capacitor and the controlled current source are connected to the array of capacitors, and the control input of the current source is connected to the

- 30 relevant control output of the control module. The array of capacitors comprises on-off switches, change-over switches and the array of capacitors whose number equals the number of bits in the digital word and a capacitance value of a capacitor of a given index is twice as high as a capacitance value of a capacitor of the previous index. The top plate of the sampling capacitor and the top plate of each capacitor in the array of capacitors are connected through the first on-off switch to the first rail and/or through the second on-off switch to the second rail and the bottom plate is connected

- through a change-over switch to ground of a circuit or to the source of auxiliary voltage. The first rail is connected to ground of the circuit through the first rail on-off switch and to the non-inverting input of the second comparator whose inverting input is connected to the source of the reference voltage. The second rail is connected to the inverting input of the first comparator whose non-inverting input is connected to the source of auxiliary voltage. The control inputs of the first on-off switches and the control inputs of the change-over switches in the array of capacitors are coupled together

- 40 and connected appropriately to the control outputs of the control module while the control inputs of the second on-off switches and the control input of the first rail are connected appropriately to the control outputs of the control module. The top plate of the sampling capacitor is connected to the source of converted voltage by the input on-off switch whose control input is connected to the control output of the control module. Furthermore, one end of the current source is connected to the second rail, and the other end of the current source is connected to the first rail.

- <sup>45</sup> **[0004]** In one of variants of the abovementioned apparatus, the sampling capacitor whose capacitance value is not smaller than the capacitance value of the capacitor having the highest capacitance value in the array of capacitors is connected in parallel to the capacitor of the highest capacitance value in the array of capacitors. The conversion of an instantaneous voltage value to the digital word is realized by changing states of signals from the relevant control outputs by means of the control module.

- 50 [0005] According to the invention, the method for clockless conversion of an instantaneous voltage value to a digital word consists in that the beginning and the end of a trigger signal are detected by the use of the control module and a converted voltage value is mapped by a portion of electric charge which is proportional to the converted voltage value. Electric charge is accumulated in the sampling capacitor, or in the sampling capacitor and in the capacitor of the highest capacitance value in the array of redistribution, which is connected in parallel to the sampling capacitor, by parallel

- <sup>55</sup> connection of the sampling capacitor, or of the sampling capacitor and of the capacitor of the highest capacitance value in the array of redistribution to the source of converted voltage during the trigger signal. Then, the process of redistribution of the accumulated electric charge is realized in the array of redistribution in a known way by changing states of signals from the relevant control outputs by the use of the control module and the relevant values are assigned to bits in the

digital word by means of the control module. The array of redistribution comprises the set of on-off switches, changeover switches and capacitors while a capacitance value of each capacitor of a given index is twice as high as a capacitance value of a capacitor of the previous index.

**[0006]** The essence of the method, according to the invention, consists in that as soon as accumulation of electric charge is terminated in the sampling capacitor, or in the sampling capacitor and in the capacitor of the highest capacitance

- <sup>5</sup> charge is terminated in the sampling capacitor, or in the sampling capacitor and in the capacitor of the highest capacitance value in the array of redistribution, which is connected to the sampling capacitor in parallel, and as soon as the beginning of next trigger signal is detected by means of the control module, electric charge is accumulated in an additional sampling capacitor. Next the process of redistribution of electric charge accumulated in the additional sampling capacitor is realized and the relevant values are assigned to bits in the digital word by means of the control module. The accumulation of

- <sup>10</sup> electric charge in the additional sampling capacitor, the process of redistribution of electric charge accumulated in the additional sampling capacitor and assignment of the relevant values to bits in the digital word by means of the control module are realized as for the sampling capacitor.

**[0007]** In this method, it is possible that as soon as the accumulation of electric charge is terminated in the additional sampling capacitor and as soon as the beginning of the next trigger signal is detected by means of the control module,

<sup>15</sup> the next cycle begins and electric charge is accumulated again in the additional sampling capacitor, or in the sampling capacitor and in the capacitor of the highest capacitance value in the array of redistribution, which is connected to the sampling capacitor in parallel.

**[0008]** In this method, it is possible that in a period of time when electric charge is accumulated in the additional sampling capacitor, electric charge is accumulated in the additional capacitor having the highest capacitance value in the array of radiatribution which is connected to the additional capacitor and to the capacitar and to the

- 20 the array of redistribution which is connected to the additional sampling capacitor and to the source of converted voltage in parallel. A capacitance value of the additional capacitor having the highest capacitance value in the array of redistribution equals the capacitance value of the capacitor having the highest capacitance value in the array of redistribution. [0009] In this method it is also possible that as soon as the process of redistribution is terminated, the portion of electric charge, accumulated in the last of capacitors on which reference voltage had not been reached when the process of

- 25 redistribution was realized, is conserved. This portion of electric charge is taken into account when the next process of redistribution is realized.

**[0010]** The apparatus, according to the invention, comprises the array of redistribution whose control inputs are connected to control outputs of the control module. The control module is equipped with the digital output, the complete conversion signal output, the trigger input, the first control input which is connected to the output of the first comparator

- 30 and the other control input which is connected to the output of the second comparator. The source of auxiliary voltage, the section of the sampling capacitor and the controlled current source whose control input is connected to the relevant output controlling current source are connected to the array of redistribution. The first end of the current source is connected to the source rail and the other end of the current source is connected to the destination rail. The array of redistribution comprises the sections whose number equals the number of bits in the digital word. The section of the

- <sup>35</sup> sampling capacitor and each section of the array of redistribution comprises the source on-off switch, the destination on-off switch, the ground change-over switch and at least one capacitor. The top plate of the sampling capacitor and the top plate of each capacitor in the array of redistribution is connected through the source on-off switch to the source rail and/or through the destination on-off switch to the destination rail and the bottom plate is connected through the ground change-over switch to ground of the circuit or to the source of auxiliary voltage. In the array of redistribution, a

- 40 capacitance value of each capacitor of a given index is twice as high as a capacitance value of a capacitor of the previous index. Moreover the top plate of the sampling capacitor is connected to the source of converted voltage trough the input on-off switch whose control input is connected to the output controlling the input on-off switch. The destination rail is connected through the on-off switch of the destination rail to ground of the circuit and is also connected to the non-inverting input of the second comparator whose inverting input is connected to the source of the reference voltage. The

- <sup>45</sup> source rail is connected to the inverting input of the first comparator whose non-inverting input is connected to the source of auxiliary voltage. The control inputs of the source on-off switches and the control input of the on-off switch of the destination rail are connected appropriately to control outputs of the control module. The control inputs of destination on-off switches and the control inputs of the ground change-over switches are coupled together and connected appropriately to the control outputs of the control module.

- <sup>50</sup> **[0011]** A significant innovation of the apparatus is that the section of the sampling capacitor comprises the additional sampling capacitor, the top plate change-over switches and the bottom plate change-over switches. The top plate of the sampling capacitor and the top plate of the additional sampling capacitor are connected to the source on-off switch and to the destination on-off switch or to the input on-off switch through the top plate change-over switches. The bottom plate of the sampling capacitor and the bottom plate of the additional sampling capacitor are connected to the ground change-over switches.

- <sup>55</sup> over switch or to ground of the circuit by the bottom plate change-over switches. The control inputs of the top plate change-over switches and the control inputs of the bottom plate change-over switches are coupled together and connected to the output controlling change-over switches of plates.

[0012] It is advantageous if at least one section of the array of redistribution comprises the additional capacitor and

the top plate change-over switches and the bottom plate change-over switches. The top plate of the capacitor and the top plates of the additional capacitor of such section are connected to the source on-off switch and to the destination on-off switch or to an input on-off switch through the top plate change-over switches. The bottom plate of the capacitor and the bottom plate of the additional capacitor of such section are connected to the ground change-over switch or to an explicit or to the additional capacitor of such section are connected to the ground change-over switch or to the additional capacitor of such section are connected to the ground change-over switch or to the additional capacitor of such section are connected to the ground change-over switch or to the additional capacitor of such section are connected to the ground change-over switch or to the additional capacitor of such section are connected to the ground change-over switch or to the additional capacitor of such section are connected to the ground change-over switch or to the ground change-over switch or to additional capacitor of such section are connected to the ground change-over switch or to additional capacitor of such section are connected to the ground change-over switch or to additional capacitor of such section are connected to the ground change-over switch or to additional capacitor of such section are connected to the ground change-over switch or to additional capacitor of such section are connected to the ground change-over switch or to additional capacitor of such section are connected to the ground change-over switch or to additional capacitor of such section are connected to the ground change-over switch or to additional capacitor of such section are connected to the ground change-over switch or to additional capacitor of such section are connected to the ground change-over switch or to additional capacitor of such section are connected to the ground change-over switch or to additional capacitor of such section are connected t

<sup>5</sup> ground of the circuit through the bottom plate change-over switches. The control inputs of the change-over top plate switches and the control inputs of bottom plate change-over switches are coupled together and connected to the output controlling change-over switches of plates.

**[0013]** It is advantageous if the capacitance values of the sampling capacitor and of the additional sampling capacitor are not smaller than the capacitance value of the capacitor having the highest capacitance value in the array of redistribution.

**[0014]** It is also advantageous if the capacitance value of the additional capacitor in the array of redistribution equals appropriately the capacitance value of the capacitor in the array of redistribution.

**[0015]** A use of an additional sampling capacitor enables realization of two successive sampling phases of converted voltage without the need to introduce a break to realize the process of redistribution of the accumulated charge and the

- relaxation phase between those two phases. The accumulation of a portion of electric charge representing the value of the second sample in the additional sampling capacitor is realized simultaneously to the process of redistribution of the portion of charge in the sampling capacitor while this portion of charge represents the first sample. In this way, the results of each conversion are presented with minimal delay equal to the time of realization of the process of charge redistribution. Moreover, the realization of actions related to the conversions of both voltage samples by the same control module, by

- 20 the array of redistribution, by the set of comparators and by the current source contributes to a reduction of amount of energy consumed per single conversion by the apparatus and in this way increases energy efficiency of its operation. [0016] A start of a new sampling phase of converted voltage after the end of the actual sampling phase enables achievement of the maximum frequency of collecting and converting a sequence of samples by means of a single apparatus. The need of breaks between following sampling phases introduced to realize the process of redistribution of

- 25 the accumulated electric charge and to realize the relaxation phase is avoided. [0017] A use of an additional capacitor having the highest capacitance value in the array of redistribution allows the required capacitance value of the sampling capacitor to be reduced twice and enables a significant reduction of area occupied by a converter produced in a form of the monolithic integrated circuit. Due to a parallel connection of the additional sampling capacitor to the additional capacitor having the highest capacitance value in the array of redistribution,

- 30 the maximum voltage value created on the additional sampling capacitor having the reduced capacitance value is not increased. Furthermore the time of realization of redistribution of charge, accumulated in the additional sampling capacitor and in the additional capacitor having the highest capacitance value in the array of redistribution connected to the additional sampling capacitor in parallel, is smaller at least by 25%.

- [0018] Conserving in the apparatus a small portion of charge which has not been taken into consideration in the value of a digital word is also an advantage. The inclusion of the abovementioned portion of charge during the process of redistribution of the subsequent accumulated charge value causes that the average value of digital output represents the average value of samples with the resolution defined by the quantization error.

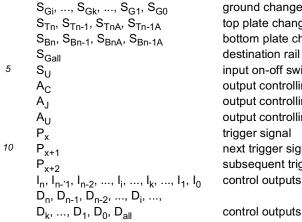

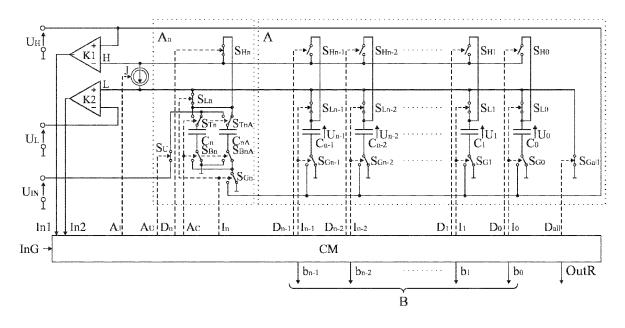

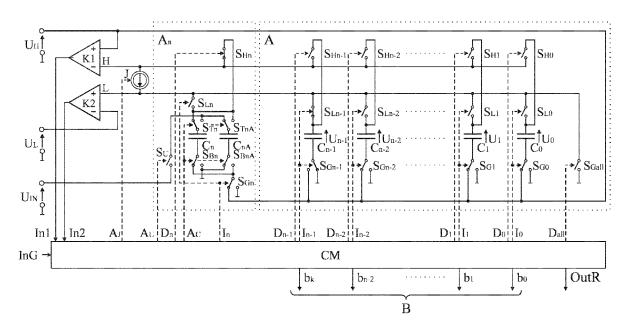

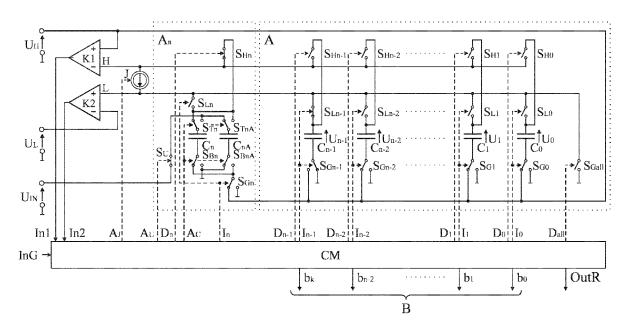

**[0019]** The subject of the invention is explained in the exemplary realizations by means of figures where the apparatus is shown at different phases of conversion process represented by different states of on-off switches and change-over switches:

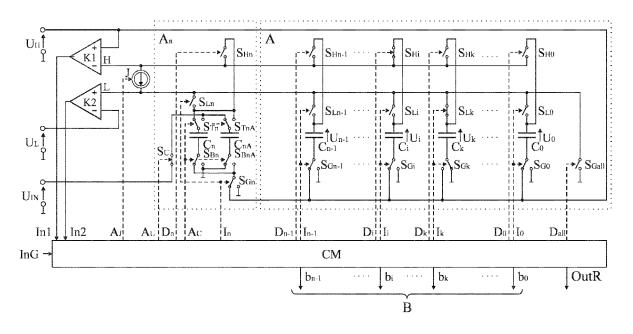

Fig. 1 illustrates the schematic diagram of the apparatus in the phase of relaxation before the beginning of the first conversion process.

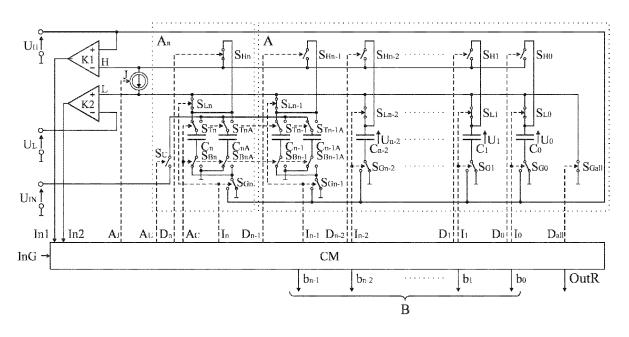

- Fig. 2 illustrates the schematic diagram of the apparatus during accumulation of electric charge in the sampling capacitor C<sub>n</sub>.

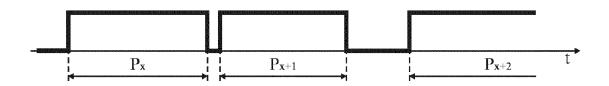

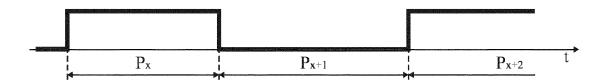

- Fig. 3 illustrates exemplary sequence of trigger signals.

10

40

<sup>50</sup> Fig. 4 illustrates exemplary sequence of trigger signals which occur immediately after themselves.

Fig. 5 illustrates the schematic diagram at the beginning of redistribution of charge accumulated in the sampling capacitor  $C_n$ .

<sup>55</sup> Fig. 6 illustrates the schematic diagram at the beginning of redistribution of charge accumulated in the sampling capacitor  $C_n$  and simultaneous accumulation of charge in the additional sampling capacitor  $C_{nA}$ .

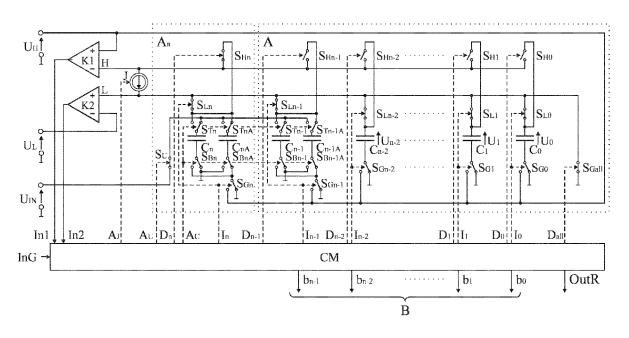

Fig. 7 illustrates the schematic diagram of the apparatus during the charge transfer from the source capacitor C<sub>i</sub> to

the destination capacitor C<sub>k</sub> and simultaneous accumulation of charge in the additional sampling capacitor C<sub>nA</sub>.

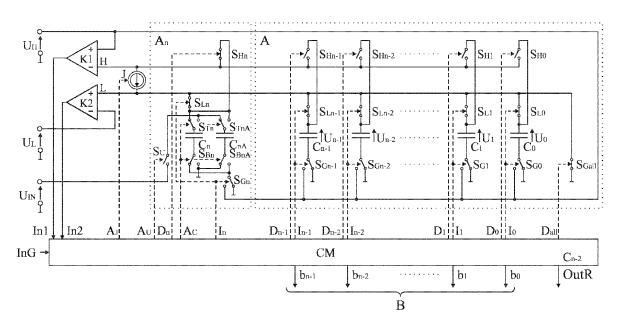

Fig. 8 illustrates the schematic diagram of the other version of apparatus in a relaxation phase before the beginning of the first conversion process.

5

Fig. 9 illustrates the schematic diagram of the other version of apparatus during accumulation of charge in the sampling capacitor  $C_n$  and in the capacitor  $C_{n-1}$  which is connected to the sampling capacitor  $C_n$  in parallel.

**[0020]** According to the invention, the method for the clockless conversion of instantaneous voltage value to a digital word consists in that the beginning and the end of the trigger signal  $P_x$  are detected by the use of the control module CM and the converted voltage value  $U_{|N}$  is mapped by a portion of electric charge which is proportional to that converted voltage value. Electric charge is accumulated in the sampling capacitor  $C_n$  by parallel connection of the sampling capacitor  $C_n$  to the source of converted voltage  $U_{|N}$  during the trigger signal  $P_x$ . Then, the process of redistribution of the accumulated charge is realized in the array of redistribution A by means of the control module CM by changing the states of the signals

- <sup>15</sup> from the relevant control outputs and the relevant values are assigned to the bits  $b_{n-1}$ ,  $b_{n-2}$ , ...,  $b_1$ ,  $b_0$  in digital word by means of the control module CM. The array of redistribution A comprises the set of on-off switches, of change-over switches and of capacitors while a capacitance value of a capacitor of a given index is twice as high as a capacitance value of a capacitor of the previous index. As soon as accumulation of charge in the sampling capacitor  $C_n$  is terminated and when the beginning of next trigger signal  $P_{x+1}$  is detected by means of the control module CM, the charge is

- <sup>20</sup> accumulated in the additional sampling capacitor  $C_{nA}$ . Next, the process of redistribution of charge accumulated in the additional sampling capacitor  $C_{nA}$  is realized and the relevant values are assigned to the bits  $b_{n-1}$ ,  $b_{n-2}$ , ...,  $b_1$ ,  $b_0$  in the digital word by means of the control module CM. The accumulation of charge in the additional sampling capacitor  $C_{nA}$ , the process of redistribution of charge accumulated in the additional sampling capacitor  $C_{nA}$ , the process of redistribution of charge accumulated in the additional sampling capacitor  $C_{nA}$  and the assignment of relevant values to the bits  $b_{n-1}$ ,  $b_{n-2}$ , ...,  $b_1$ ,  $b_0$  in the digital word are realized in the same way as for the sampling capacitor  $C_{nA}$  and the assignment of relevant values to the bits  $b_{n-1}$ ,  $b_{n-2}$ , ...,  $b_1$ ,  $b_0$  in the digital word are realized in the same way as for the sampling capacitor  $C_{nA}$ .

25 C<sub>n</sub>.

**[0021]** The another exemplary solution is **characterized in that** as soon as accumulation of electric charge in the additional sampling capacitor  $C_{nA}$  is terminated and when the beginning of the subsequent trigger signal  $P_{x+2}$  is detected by means of the control module CM, the next cycle begins and the charge is accumulated in the sampling capacitor  $C_n$  again.

- <sup>30</sup> **[0022]** The another exemplary solution is **characterized in that** during the next trigger signal  $P_{x+1}$  when the charge is accumulated in the additional sampling capacitor  $C_{nA}$ , the delivered charge is accumulated simultaneously in the additional capacitor  $C_{n-1A}$  having the highest capacitance value in the array of redistribution which is connected to the additional sampling capacitor  $C_{nA}$  and to the source of converted voltage  $U_{IN}$  in parallel. The capacitance value of the additional capacitor  $C_{n-1A}$  having the highest capacitance value in the array of redistribution is equal to the capacitance value of the capacitor  $C_{n-1A}$  having the highest capacitance value in the array of redistribution.

- **[0023]** The another exemplary solution is **characterized in that** as soon as the process of redistribution is terminated in the last of capacitors on which reference voltage  $U_L$  had not been reached when the process of redistribution is realized, the charge accumulated in the last of capacitors is conserved.

[0024] In detail, the abovementioned process of redistribution in the exemplary solution is presented as follows.

- <sup>40</sup> **[0025]** As soon as accumulation of electric charge in the sampling capacitor  $C_n$  is terminated, the function of the source capacitor  $C_i$ , whose index is defined by the content of the source index register, is assigned by means of the control module CM to the sampling capacitor  $C_n$  by writing the value of the index of the sampling capacitor  $C_n$  to this register. Simultaneously, the function of the destination capacitor  $C_k$ , whose index is defined by the content of the destination index register, is assigned by means of the control module CM to the capacitor  $C_{n-1}$  having the highest capacitance

- <sup>45</sup> value in the array of redistribution by writing the value of the index of the capacitor  $C_{n-1}$  to this register. Then, the process of redistribution of the accumulated charge is realized by transfer of the charge from the source capacitor  $C_i$  to the destination capacitor  $C_k$  by the use of the current source J. At the same time, the voltage  $U_k$  increasing on the destination capacitor  $C_k$  is compared to the reference voltage  $U_L$  by the use of the second comparator K2, and also the voltage  $U_i$ on the source capacitor  $C_i$  is observed by the use of the first comparator K1.

- <sup>50</sup> **[0026]** When the voltage U<sub>i</sub> on the source capacitor C<sub>i</sub> observed by the use of the first comparator K1 equals zero during the charge transfer, the function of the source capacitor C<sub>i</sub> is assigned to the current destination capacitor C<sub>k</sub> by means of the control module CM on the basis of the output signal of the first comparator K1 by writing the current content of the destination index register to the source index register, and the function of the destination capacitor C<sub>k</sub> is assigned to the subsequent capacitor in the array of redistribution A whose capacitance value is twice lower than the capacitance

- <sup>55</sup> value of the capacitor that acted as the destination capacitor directly before by reducing the content of the destination index register by one, and the charge transfer from a new source capacitor  $C_i$  to a new destination capacitor  $C_k$  is continued by the use of the current source J.

[0027] When the voltage  $U_k$  on the destination capacitor  $C_k$  observed by the use of the second comparator K2 equals

the reference voltage  $U_L$  during the transfer of charge from the source capacitor  $C_i$  to the destination capacitor  $C_k$ , the function of the destination capacitor  $C_k$  is assigned by means of the control module CM on the basis of the output signal of the second comparator K2 to the subsequent capacitor in the array of redistribution A whose capacitance value is twice lower than the capacitance value of the capacitor that acted as the destination capacitor directly before by reducing

- the content of the destination index register by one, and also the charge transfer from the source capacitor C<sub>i</sub> to a new destination capacitor C<sub>k</sub> is continued.

[0028] The process of redistribution is still controlled by means of the control module CM on the basis of the output signals of both comparators (K1 and K2) until the voltage U<sub>i</sub> on the source capacitor C<sub>i</sub> observed by the use of the first

- comparator K1 equals zero during the period of time when the function of the destination capacitor  $C_k$  is assigned to the capacitor  $C_0$  having the lowest capacitance value in the array of redistribution, or the voltage  $U_0$  increasing on the capacitor  $C_0$  having the lowest capacitance value in the array of redistribution and observed at the same time by the use of the second comparator K2 equals the reference voltage  $U_L$ . The value one is assigned to the bits in the digital word corresponding to the capacitors in the array of redistribution on which the voltage equal to the reference voltage value  $U_L$  has been obtained, and the value zero is assigned to the other bits by means of the control module CM.

- <sup>15</sup> **[0029]** According to the invention, the apparatus for clockless conversion of instantaneous voltage value to the digital word comprises the array of redistribution A whose control inputs are connected to control outputs of the control module CM. The control module CM is equipped with the digital output B, the complete conversion output OutR, the trigger input InS, the first control input In1 connected to the output of the first comparator K1 and the other control input In2 connected to the output of the second comparator K2. The source of auxiliary voltage U<sub>H</sub>, the section of the sampling capacitor An

- and the controlled current source J are connected to the array of redistribution A. The control input of the current source J is connected to the output controlling the current source A<sub>J</sub>. The first end of the current source J is connected to the source rail H and the other end of the current source J is connected to the destination rail L. The array of redistribution comprises the sections whose number n equals the number of bits in the digital word.

- [0030] The section of the sampling capacitor An and the sections of the array of redistribution A comprise the source on-off switches S<sub>Hn</sub>; S<sub>Hn-1</sub>, S<sub>Hn-2</sub>, ..., S<sub>H1</sub>, S<sub>H0</sub>, the destination on-off switches S<sub>Ln</sub>; S<sub>Ln-1</sub>, S<sub>Ln-2</sub>, ..., S<sub>L1</sub>, S<sub>L0</sub>, the ground change-over switches S<sub>Gn</sub>; S<sub>Gn-1</sub>, S<sub>Gn-2</sub>, ..., S<sub>G1</sub>, S<sub>G0</sub> and the capacitors C<sub>n</sub>; C<sub>n-1</sub>, C<sub>n-2</sub>, ..., C<sub>1</sub>, C<sub>0</sub>. The top plates of the capacitors C<sub>n-1</sub>, C<sub>n-2</sub>, ..., C<sub>1</sub>, C<sub>0</sub> of the array of redistribution are connected to the source rail H by the use of the source on-off switches S<sub>Hn-1</sub>, S<sub>Hn-2</sub>, ..., S<sub>H1</sub>, S<sub>H0</sub> and to the destination rail L by the use of the destination on-off switches S<sub>Ln-1</sub>, S<sub>Ln-2</sub>, ..., S<sub>L1</sub>, S<sub>L0</sub>. The bottom plates of these capacitors are connected to ground of the circuit and to the source of

- <sup>30</sup> auxiliary voltage U<sub>H</sub> by the use of the ground change-over switches S<sub>Gn-1</sub>, S<sub>Gn-2</sub>, ..., S<sub>G1</sub>, S<sub>G0</sub>. In the array of redistribution A, a capacitance value of each capacitor C<sub>n-1</sub>, C<sub>n-2</sub>, ..., C<sub>1</sub>, C<sub>0</sub> of a given index is twice as high as a capacitance value of a capacitor of the previous index. The capacitance value of the sampling capacitor C<sub>n</sub> is twice as high as the capacitance value of the capacitor C<sub>n</sub> having the highest capacitance value in the array of redistribution. The relevant bit b<sub>n-1</sub>, b<sub>n-2</sub>, ..., b<sub>1</sub>, b<sub>0</sub> in the digital word is assigned to each capacitor C<sub>n-1</sub>, C<sub>n-2</sub>, ..., C<sub>1</sub>, C<sub>0</sub> in the array of redistribution. The destination

- <sup>35</sup> rail L is connected through the on-off switch of the destination rail S<sub>Gall</sub> to ground of the circuit and is also connected to the non-inverting input of the second comparator K2 whose inverting input is connected to the source of the reference voltage U<sub>L</sub>. The source rail H is connected to the inverting input of the first comparator K1 whose non-inverting input is connected to the source of auxiliary voltage U<sub>H</sub>. The control inputs of the source on-off switches S<sub>Hn</sub>; S<sub>Hn-1</sub>, S<sub>Hn-2</sub>, ..., S<sub>H1</sub>, S<sub>H0</sub> and the control inputs of the on-off switch of the destination rail S<sub>Gall</sub> are connected appropriately to the control

- outputs D<sub>n</sub>; D<sub>n-1</sub>, D<sub>n-2</sub>, ..., D<sub>1</sub>, D<sub>0</sub>; D<sub>all</sub>. The control inputs of the destination on-off switches S<sub>Ln</sub>; S<sub>Ln-1</sub>, S<sub>Ln-2</sub>, ..., S<sub>L1</sub>, S<sub>L0</sub> and the control inputs of the ground change-over switches S<sub>Gn</sub>; S<sub>Gn-1</sub>, S<sub>Gn-2</sub>, ..., S<sub>G1</sub>, S<sub>G0</sub> are coupled together and connected appropriately to the control outputs I<sub>n</sub>; I<sub>n-1</sub>, I<sub>n-2</sub>, ..., I<sub>1</sub>, I<sub>0</sub>.

[0031] The section of the sampling capacitor An comprises also the additional sampling capacitor C<sub>nA</sub>, the top plate

- change-over switches  $S_{Tn}$ ,  $S_{TnA}$ , the bottom plate change-over switches  $S_{Bn}$ ,  $S_{BnA}$  and the input on-off switch  $S_u$  whose control input is connected to the output controlling the input on-off switch  $A_U$ . The capacitance value of the additional sampling capacitor  $C_{nA}$  is equal to the capacitance value of the sampling capacitor  $C_n$ . The top plate of the sampling capacitor  $C_n$  and the top plate of the additional sampling capacitor  $C_{nA}$  are connected to the source on-off switch  $S_{Hn}$ , to the destination on-off switch  $S_{Ln}$  and to the input on-off switch  $S_U$  through the top plate change-over switches  $S_{Tn}$ ,  $S_{TnA}$ . The bottom plates of the sampling capacitor  $C_n$  and the bottom plates of the additional sampling capacitor  $C_{nA}$

- <sup>50</sup> are connected to the ground change-over switch S<sub>Gn</sub> and to ground of the circuit through the bottom plate change-over switches S<sub>Bn</sub>, S<sub>BnA</sub>. The control inputs of the top plate change-over switches S<sub>Tn</sub>, S<sub>TnA</sub> and the control inputs of the bottom plate change-over switches S<sub>Bn</sub>, S<sub>BnA</sub>. The control inputs of the top plate change-over switches S<sub>Tn</sub>, S<sub>TnA</sub> and the control inputs of the bottom plate change-over switches S<sub>Bn</sub>, S<sub>BnA</sub> are coupled together and connected to the output controlling the change-over switches of plates A<sub>C</sub>. The source on-off switch S<sub>Hn</sub> is connected to the source rail H, the destination on-off switch S<sub>Ln</sub> is connected to the destination rail L, the input on-off switch S<sub>U</sub> is connected to the source of the converted voltage

- <sup>55</sup> U<sub>IN</sub> and the ground change-over switch S<sub>Gn</sub> is connected to ground of the circuit and to the source of auxiliary voltage U<sub>H</sub>. [0032] In the another exemplary solution, the section of the capacitor C<sub>n-1</sub> having the highest capacitance value in the array of redistribution comprises the additional capacitor C<sub>n-1A</sub> having the highest capacitance value in the array of redistribution, the top plate change-over switches S<sub>Tn-1</sub>. S<sub>Tn-1A</sub> and the bottom plate change-over switches S<sub>Bn-1</sub>, S<sub>Bn-1A</sub>.

The capacitance value of the additional capacitor  $C_{n-1A}$  having the highest capacitance value in the array of redistribution is equal to the capacitance value of the capacitor  $C_{n-1}$  having the highest capacitance value in the array of redistribution. The top plates of the capacitor  $C_{n-1}$  having the highest capacitance value in the array of redistribution and the top plates of the additional capacitor  $C_{n-1A}$  having the highest capacitance value in the array of redistribution and the top plates of the additional capacitor  $C_{n-1A}$  having the highest capacitance value in the array of redistribution and the top plates of the additional capacitor  $C_{n-1A}$  having the highest capacitance value in the array of redistribution are connected to the

- <sup>5</sup> source on-off switch  $S_{Hn-1}$ , to the destination on-off switch  $S_{Ln-1}$  and to the input on-off switch  $S_U$  by the use of the top plate change-over switches  $S_{Tn-1}$ ,  $S_{Tn-1A}$ . The bottom plates of the capacitor  $C_{n-1}$  having the highest capacitance value in the array of redistribution and the top plates of the additional capacitor  $C_{n-1A}$  having the highest capacitance value in the array of redistribution are connected to the ground change-over switch  $S_{Gn-1}$  and to ground of the circuit through the bottom plate change-over switches  $S_{Bn-1}$   $S_{Bn-1A}$ . The control inputs of the top plate change-over switches  $S_{Tn-1}$ ,  $S_{Tn-1A}$ .

- and the control inputs of the bottom plate change-over switches S<sub>Bn-1</sub>, S<sub>Bn-1A</sub> are coupled together and connected to the output controlling the change-over switches of plates A<sub>C</sub>.

[0033] The method for conversion of an instantaneous voltage value to the digital word, according to the invention, is presented in the first exemplary apparatus as follows. Before the first process of conversion of an instantaneous voltage value to the digital word having the number of bits equal to n, the control module CM introduces the complete conversion

- <sup>15</sup> output OutR to the inactive state. The control module CM causes the opening of the input on-off switch  $S_U$  and the disconnection of the source of converted voltage  $U_{IN}$  from the top plate change-over switches  $S_{Tn}$ ,  $S_{TnA}$  by the use of the signal from the output controlling the input on-off switch  $A_U$ . The control module CM also causes the switching off the current source J by the use of the signal from the output controlling the change-over switches of plates  $A_C$ , the control module CM causes the switching of the

- <sup>20</sup> top plate change-over switches  $S_{Tn}$ ,  $S_{TnA}$  and of the bottom plate change-over switches  $S_{Bn}$ ,  $S_{BnA}$  and the connection of the top plate of the sampling capacitor  $C_n$  to the source on-off switch  $S_{Hn}$  and to the destination on-off switch  $S_{Ln}$ , the connection of the top plate of the additional sampling capacitor  $C_{nA}$  to the input on-off switch  $S_U$ , the connection of the bottom plate of the sampling capacitor  $C_n$  to the ground change-over switch  $S_{Gn}$  and the connection of the bottom plate of the additional sampling capacitor  $C_n$  to ground of the circuit.

- [0034] Next the control module CM introduces the apparatus into the relaxation state shown in fig.1. Therefore, the control module CM causes the opening of the source on-off switches S<sub>Hn-1</sub>, S<sub>Hn-2</sub>, ..., S<sub>H1</sub>, S<sub>H0</sub> by the use of the signals from the control outputs D<sub>n-1</sub>, D<sub>n-2</sub>, ..., D<sub>1</sub>, Do. Furthermore, by the use of the signals from the control outputs I<sub>n</sub>; I<sub>n-1</sub>, I<sub>n-2</sub>,..., I<sub>1</sub>, I<sub>0</sub>, the control module CM causes the closure of the destination on-off switches S<sub>Ln</sub>; S<sub>Ln-1</sub>, S<sub>Ln-2</sub>, ..., S<sub>L1</sub>, S<sub>L0</sub> and the connection of the top plate of the sampling capacitor C<sub>n</sub> and the top plates of all the capacitors C<sub>n-1</sub>, C<sub>n-2</sub>, ...,

- <sup>30</sup>  $C_1, C_0$  in the array of redistribution to the destination rail L, the switching of the ground change-over switches  $S_{Gn}$ ;  $S_{Gn-1}$ ,  $S_{Gn-2}, ..., S_{G1}, S_{G0}$  and the connection of the bottom plate of the sampling capacitor  $C_n$  and the bottom plates of all the capacitors  $C_{n-1}, C_{n-2}, ..., C_1, C_0$  in the array of redistribution to ground of the circuit. By the use of the signal from the control output  $D_{all}$ , the control module CM causes the closure of the destination rail on-off switch  $S_{Gall}$  and the connection of the circuit enforcing a complete discharge of the sampling capacitor  $C_n$  and of all

- <sup>35</sup> the capacitors  $C_{n-1}$ ,  $C_{n-2}$ , ...,  $C_1$ ,  $C_0$  in the array of redistribution. At the same time, by the use of signal from the control output  $D_n$ , the control module CM causes the closure of the source on-off switch  $S_{Hn}$  and the connection of the source rail H to the destination rail L and to ground of the circuit which prevents the occurrence of a random potential on the source rail H.

- **[0035]** As soon as the beginning of the trigger signal  $P_x$  is detected on the trigger input InS by the module CM, the apparatus is introduced into the state shown in fig. 2 by the use of the module CM. Therefore, by the use of the signal from the output controlling the change-over switches of plates  $A_c$ , the control module CM causes the switching of the top plate change-over switches  $S_{Tn}$ ,  $S_{TnA}$  and switching of the bottom plate change-over switches  $S_{Bn}$ ,  $S_{BnA}$  and the connection of the top plate of the sampling capacitor  $C_n$  to the input on-off switch  $S_U$ , the connection of the top plate of the additional sampling capacitor  $C_{nA}$  to the source on-off switch  $S_{Hn}$  and to the destination on-off switch  $S_{Ln}$ , the

- <sup>45</sup> connection of the bottom plate of the sampling capacitor  $C_n$  to ground of the circuit and the connection of the bottom plate of the additional sampling capacitor  $C_{nA}$  to the ground change-over switch  $S_{Gn}$  enforcing a complete discharge of the additional sampling capacitor  $C_{nA}$ . Then, the control module CM causes the closure of the input on-off switch  $S_U$ and the connection of the source of converted voltage  $U_{IN}$  to the top plate change-over switches  $S_{Tn}$ ,  $S_{TnA}$  by the use of the signal from the output controlling the input on-off switch  $A_U$ . The charge is accumulated in the sampling capacitor

- $C_n$  which as the only capacitor is then connected to the source of converted voltage U<sub>IN</sub> in parallel through the top plate change-over switch S<sub>Tn</sub> and through the input on-off switch S<sub>U</sub>, and also through the bottom plate change-over switch S<sub>Bn</sub> and ground of the circuit.

55

**[0036]** As soon as the end of the trigger signal  $P_x$  is detected by the control module CM on the trigger input InS, the control module CM by the use of the signal from the control output  $D_{all}$  causes the opening of the destination rail on-off switch  $S_{Gall}$  and the disconnection of the destination rail L from ground of the circuit. By the use of the signals from

control outputs  $I_n$ ;  $I_{n-2}$ , ...,  $I_1$ ,  $I_0$ , the control module CM causes the opening of the destination on-off switches  $S_{Ln}$ ;  $S_{Ln-2}$ , ...,  $S_{L1}$ ,  $S_{L0}$  and the disconnection of the top plates of the additional sampling capacitor  $C_{nA}$  and of the capacitors  $C_{n-2}$ ,...,  $C_1$ ,  $C_0$  in the array of redistribution from the destination rail L, the switching of the ground change-over switches  $S_{Gn}$ ;

7

$S_{Gn-2}, ..., S_{G1}, S_{G0}$  and the connection of the bottom plates of the additional sampling capacitor  $C_{nA}$  and of the capacitors  $C_{n-2}, ..., C_1, C_0$  in the array of redistribution to the source of auxiliary voltage  $U_H$ . By the use of the signal from the output controlling the change-over switches of plates  $A_C$ , the control module CM causes the switching of the top plate change-over switches  $S_{Tn}, S_{TnA}$  and of the bottom plate change-over switches  $S_{Bn}, S_{BnA}$  and the connection of the top plate of

- <sup>5</sup> the sampling capacitor  $C_n$  to the source on-off switch  $S_{Hn}$  and to the destination on-off switch  $S_{Ln}$ , the connection of the top plate of the additional sampling capacitor  $C_{nA}$  to the input on-off switch  $S_U$ , the connection of the bottom plate of the sampling capacitor  $C_n$  to the ground change-over switch  $S_{Gn}$  and the connection of the bottom plate of the additional sampling capacitor  $C_{nA}$  to ground of the circuit.

- **[0037]** If the end of the trigger signal  $P_x$  detected by the control module CM does not constitute the beginning of the next trigger signal  $P_{x+1}$  as it is shown in fig. 3, the control module CM causes the opening of the input on-off switch  $S_U$  and the disconnection of the source of converted voltage  $U_{IN}$  from the top plate change-over switches  $S_{Tn}$ ,  $S_{TnA}$  by the use of the signal from the output controlling the input on-off switch  $A_U$ . The abovementioned state of the apparatus is shown in fig. 5. As soon as the beginning of the next trigger signal  $P_{x+1}$  is detected by the control module CM on the trigger input InS, by the control module CM by the use of the signal from the output con-off switch

- <sup>15</sup> A<sub>U</sub> causes again the closure of the input on-off switch S<sub>U</sub> and the connection of the source of converted voltage U<sub>IN</sub> to the top plate change-over switches S<sub>Tn</sub>, S<sub>TnA</sub>. The charge is accumulated in the additional sampling capacitor C<sub>nA</sub> which as the only capacitor is then connected to the source of converted voltage U<sub>IN</sub> through the top plate change-over switch S<sub>TnA</sub> and the input on-off switch S<sub>U</sub> and through the bottom plate change-over switch S<sub>BnA</sub> and ground of the circuit. **[0038]** If the end of the trigger signal P<sub>x</sub> detected by the control module CM determines simultaneously the beginning

- of the next trigger signal  $P_{x+1}$  as it is shown in fig. 4, the charge is accumulated in the additional sampling capacitor  $C_{nA}$ which as the only capacitor is then connected to the source of converted voltage  $U_{IN}$  through the top plate change-over switch  $S_{TnA}$  and the input on-off switch  $S_U$  and through the bottom plate change-over switch  $S_{BnA}$  and ground of the circuit. The abovementioned state of the apparatus is shown in fig. 6.

- **[0039]** In both cases, the control module CM introduces the complete conversion output OutR into the inactive state and assigns the initial value zero to all the bits  $b_{n-1}$ ,  $b_{n-2}$ , ...,  $b_1$ ,  $b_0$  in the digital word. Then, the control module CM assigns the function of the source capacitor  $C_i$  to the sampling capacitor  $C_n$  by writing the value of the index of the sampling capacitor to the source index register. Simultaneously, the control module CM assigns the function of the destination capacitor  $C_k$  to the capacitor  $C_{n-1}$  having the highest capacitance value in the array of redistribution by writing the value of the index of the capacitor having the highest capacitance value in the array of redistribution to the destination

- <sup>30</sup> index register. Next, the control module CM starts to realize the process of redistribution of the accumulated electric charge. Therefore, the control module CM by the use of the signal from the output controlling current source  $A_J$  causes the switching on the current source J. The charge accumulated in the source capacitor  $C_i$  is transferred to the destination capacitor  $C_k$  by the use of the current source J though the source rail H and the destination rail L and the voltage  $U_i$  on the source capacitor gradually decreases and at the same time the voltage  $U_k$  on the destination capacitor gradually increases during the charge transfer.

- **[0040]** In case when the voltage  $U_k$  on the current destination capacitor  $C_k$  reaches the reference voltage  $U_L$  value, then the value one is assigned by the control module CM to the appropriate bit  $b_k$  in the digital word on the basis of the output signal of the second comparator K2. By the use of the signal from the control output  $I_k$ , the control module CM causes the opening of the destination on-off switch  $S_{Lk}$  and the disconnection of the top plate of the destination capacitor

- <sup>40</sup> C<sub>k</sub> from the destination rail L, the simultaneous switching of the ground change-over switch S<sub>Gk</sub> and the connection of the bottom plate of the destination capacitor C<sub>k</sub> to the source of auxiliary voltage U<sub>H</sub>. Next, the control module CM assigns the function of the destination capacitor C<sub>k</sub> to the subsequent capacitor in the array of redistribution A whose capacitance value is twice lower than the capacitance value of the capacitor that acted as the destination comparator C<sub>k</sub> directly before by reducing the content of the destination index register by one. By the use of the signal from the control output

- <sup>45</sup> I<sub>k</sub>, the control module CM causes the closure of the destination on-off switch S<sub>Lk</sub> and the connection of the top plate of a new destination capacitor C<sub>k</sub> to the destination rail L, the simultaneous switching of the ground change-over switch S<sub>Gk</sub> and the connection of the bottom plate of the destination capacitor C<sub>k</sub> to ground of the circuit. **[0041]** In case when the voltage U<sub>i</sub> on the source capacitor reaches the value zero during charge transfer, then on

- the basis of the output signal of the first comparator K1 the control module CM by the use of the signal from the control output D<sub>i</sub> causes the opening of the source on-off switch S<sub>Hi</sub> and the disconnection of the top plate of the source capacitor C<sub>i</sub> from the source rail H. By the use of the signal from the control output I<sub>k</sub>, the control module CM causes the opening of the destination on-off switch S<sub>Lk</sub> and the disconnection of the top plate of the destination capacitor C<sub>k</sub> from the destination rail L, the simultaneous switching of the ground change-over switch S<sub>Gk</sub> and the connection of the bottom plate of the destination capacitor C<sub>k</sub> to the source of auxiliary voltage U<sub>H</sub>. Next, the function of the source capacitor C<sub>i</sub>

- <sup>55</sup> is assigned by the control module CM to the capacitor that acted as the destination capacitor  $C_k$  directly before by writing the current content of the destination index register to the source index register. The control module CM by the use of the signal from the control output  $D_i$  causes the closure of the source on-off switch  $S_{Hi}$  and the connection of the top plate of a new source capacitor  $C_i$  to the source rail H. Then, the control module CM reduces the content of the destination

index register by one and assigns the function of the destination capacitor  $C_k$  to the next capacitor in the array of redistribution A having a capacitance value twice lower than the capacitance value of the capacitor that acted as the destination capacitor  $C_k$  directly before. By the use of the signal from the control output  $I_k$ , the control module CM causes the closure of the destination on-off switch  $S_{Lk}$  and the connection of the top plate of a new destination capacitor  $C_k$  to

- <sup>5</sup> the destination rail L, the simultaneous switching of the ground change-over switch S<sub>Gk</sub> and the connection of the bottom plate of a new destination capacitor C<sub>k</sub> to ground of the circuit. Fig. 7 presents the apparatus in the abovementioned state. [0042] In both abovementioned cases, the control module CM continues the process of electric charge redistribution on the basis of the output signals of the first comparator K1 and of the second comparator K2. Each occurrence of the active state on the output of the second comparator K2 causes the assignment of the function of the destination capacitor

- <sup>10</sup>  $C_k$  to the subsequent capacitor in the array of redistribution A whose capacitance value is twice as lower as the capacitance value of the capacitor which acted as the destination capacitor  $C_k$  directly before. On the other hand, each occurrence of the active state on the output of first comparator K1 causes the assignment of the function of the source capacitor  $C_i$  to the capacitor in the array of redistribution A that until now has acted as the destination capacitor  $C_k$ , and at the same time the assignment of the function of the function of the destination capacitor  $C_k$  to the subsequent capacitor in the array A whose

- <sup>15</sup> capacitance value is twice as lower as the capacitance value of the capacitor which acted as the destination capacitor directly before. The process of redistribution is terminated when the capacitor  $C_0$  having the lowest capacitance value in the array of redistribution A stops to act as the destination capacitor  $C_k$ . Such situation occurs when the active state appears on the output of the first comparator K1 or on the output of the second comparator K2 during charge transfer to the capacitor  $C_0$  having the lowest capacitance value in the array of redistribution A. When the active state appears

- <sup>20</sup> on the output of the second comparator K2, the control module CM assigns the value one to the bit  $b_0$ . After termination of redistribution of charge accumulated previously in the sampling capacitor  $C_n$  and after assigning the corresponding values to the bits  $b_{n-1}$ ,  $b_{n-2}$ , ...,  $b_1$ ,  $b_0$  in the output digital word, the control module CM activates the signal provided on the complete conversion signal output OutR. By the use of the signal from the output controlling the current source  $A_J$ , the control module CM causes the switching off the current source J. Next, the control module CM introduces the apparatus into the relaxation phase.

**[0043]** After detecting the end of the next trigger signal  $P_{x+1}$  by the control module CM on the trigger input InS, the control module CM by the use of the signal from the control output  $D_{all}$  causes the opening of the destination rail on-off switch  $S_{Gall}$  and the disconnection of the destination rail L from ground of the circuit. The control module CM by the use of signals from the control outputs  $I_n$ ;  $I_{n-2}$ , ...,  $I_1$ ,  $I_0$  causes the opening of the destination on-off switches  $S_{Ln}$ ;  $S_{Ln-2}$ , ...,

- <sup>30</sup> S<sub>L1</sub>, S<sub>L0</sub> and the disconnection of the top plates of the sampling capacitor C<sub>n</sub> and of the capacitors C<sub>n-2</sub>,..., C<sub>1</sub>, C<sub>0</sub> in the array of redistribution from the destination rail L, the switching of the ground change-over switches S<sub>Gn</sub>; S<sub>Gn-2</sub>, ..., S<sub>G1</sub>, S<sub>G0</sub> and the connection of the bottom plates of the sampling capacitor C<sub>n</sub> and of the capacitors C<sub>n-2</sub>, ..., C<sub>1</sub>, C<sub>0</sub> in the array of redistribution to the source of auxiliary voltage U<sub>H</sub>. By the use of the signal from the output controlling change-over switches S<sub>Tn</sub>, S<sub>TnA</sub>

- <sup>35</sup> and of the bottom plate change-over switches  $S_{Bn}$ ,  $S_{BnA}$  and the connection of the top plate of the sampling capacitor  $C_n$  to the input on-off switch  $S_U$ , the connection of the top plate of the additional sampling capacitor  $C_{nA}$  to the source on-off switch  $S_{Hn}$  and to the destination on-off switch  $S_{Ln}$ , the connection of the bottom plate of the sampling capacitor  $C_n$  to ground of the circuit and the connection of the bottom plate of the additional sampling capacitor  $C_n$  to the ground of the circuit and the connection of the bottom plate of the additional sampling capacitor  $C_{nA}$  to the ground change-over switch  $S_{Gn}$ .

- <sup>40</sup> **[0044]** In case when the end of the next trigger signal  $P_{x+1}$  detected by the control module CM does not constitute simultaneously the beginning of the subsequent trigger signal  $P_{x+2}$  as it is shown in fig. 3, the control module CM by the use of the signal from the output controlling the input on-off switch  $A_U$  causes the opening of the input on-off switch  $S_U$  and the disconnection of the source of converted voltage  $U_{IN}$  from the top plate change-over switches  $S_{Tn}$ ,  $S_{TnA}$ . As soon as the beginning of the subsequent trigger signal  $P_{x+2}$  is detected by the control module CM on the trigger input

- <sup>45</sup> InS, the control module CM by the use of the signal from the output controlling the input on-off switch  $A_U$  causes again the closure of the input on-off switch  $S_U$  and the connection of the source of converted voltage  $U_{IN}$  to the top plate change-over switches  $S_{Tn}$ ,  $S_{TnA}$ . The charge is accumulated in the sampling capacitor  $C_n$  which is then the only capacitor connected to the source of converted voltage  $U_{IN}$  through the top plate change-over switch  $S_{Tn}$ , the input on-off switch  $S_U$  and through the bottom plate change-over switch  $S_{Bn}$  and ground of the circuit.

- <sup>50</sup> **[0045]** In case when the end of the next trigger signal  $P_{x+1}$  detected by the control module CM constitutes simultaneously the beginning of the subsequent trigger signal  $P_{x+2}$  as it is shown in fig. 4, the electric charge is accumulated in the sampling capacitor  $C_n$  which is then the only capacitor connected to the source of converted voltage  $U_{IN}$  through the top plate change-over switch  $S_{Tn}$ , the input on-off switch  $S_U$  and through the bottom plate change-over switch  $S_{Bn}$  and ground of the circuit.

- <sup>55</sup> **[0046]** In both cases, the control module CM deactivates the signal provided on the complete conversion signal output OutR and assigns the initial value zero to all the bits  $b_{n-1}$ ,  $b_{n-2}$ , ...,  $b_1$ ,  $b_0$  in the digital word. Then, the control module CM assigns the function of the source capacitor  $C_i$  to the additional sampling capacitor  $C_{nA}$  by writing the value of the sampling capacitor  $C_n$  index to the source index register. Simultaneously, the control module CM assigns the function

of the destination capacitor  $C_k$  to the capacitor  $C_{n-1}$  having the highest capacitance value in the array of redistribution by writing a value of the index of the capacitor  $C_{n-1}$  having the highest capacitance value in the array of redistribution to the destination index register. Next, the control module CM by the use of the signal from the output controlling current source  $A_J$  causes the switching on the current source J and starts to realize the process of redistribution of charge

- <sup>5</sup> accumulated in the additional sampling capacitor  $C_{nA}$ . The process of redistribution is terminated when the capacitor  $C_0$  having the lowest capacitance value in the array of redistribution A stops to act as the destination capacitor  $C_k$ . After termination of redistribution of charge accumulated previously in the additional sampling capacitor  $C_{nA}$  and after assigning the corresponding values to the bits  $b_{n-1}$ ,  $b_{n-2}$ , ...,  $b_1$ ,  $b_0$  in the digital word, the control module CM activates the complete conversion signal output OutR. By the use of the signal from the output controlling the current source  $A_J$ , the control

- <sup>10</sup> module CM causes the switching off the current source J. Next, the control module CM introduces the apparatus into the relaxation phase.

**[0047]** According to the invention, the method for conversion of an instantaneous voltage value to the digital word realized in the second exemplary apparatus is as follows. Before the start of the first process of conversion of an instantaneous voltage value to the digital word having the number of bits equal to n, the control module CM by the use

- <sup>15</sup> of the signal from the output controlling the change-over switches of plates  $A_C$  causes additionally the switching of top plate change-over switches  $S_{Tn-1}$ ,  $S_{Tn-1A}$  and switching of the bottom plate change-over switches  $S_{Bn-1}$ ,  $S_{Bn-1A}$  and the connection of the top plate of the capacitor  $C_{n-1}$  having the highest capacitance value in the array of redistribution to the source on-off switch  $S_{Hn-1}$  and to the destination on-off switch  $S_{Ln-1}$ , the connection of the top plate of the additional capacitor  $C_{n-1A}$  having the highest capacitance value in the array of redistribution to the input on-off switch  $S_U$ , the

- <sup>20</sup> connection of the bottom plate of the capacitor  $C_{n-1}$  having the highest capacitance value in the array of redistribution to the ground change-over switch  $S_{Gn-1}$  and the connection of the bottom plate of the additional capacitor  $C_{n-1A}$  having the highest capacitance value in the array of redistribution to ground of the circuit. Fig. 8 presents the abovementioned state of the apparatus.

- **[0048]** As soon as the beginning of the next trigger signal  $P_x$  is detected by the control module CM on the trigger input InS, the control module CM by the use of the signal from the output controlling the change-over switches of plates  $A_C$ causes additionally the switching of the top plate change-over switches  $S_{Tn-1}$ ,  $S_{Tn-1A}$  and switching of the bottom plate change-over switches  $S_{B-1n}$ ,  $S_{Bn-1A}$  and the connection of the top plate of the sampling capacitor  $C_{n-1}$  having the highest capacitance value in the array of redistribution to the input on-off switch  $S_U$ , the connection of the top plate of the additional capacitor  $C_{n-1A}$  having the highest capacitance value in the array of redistribution to the source on-off switch  $S_{Hn-1}$  and

- 30 to the destination on-off switch S<sub>Ln-1</sub>, the connection of the bottom plate of the sampling capacitor C<sub>n-1</sub> having the highest capacitance value in the array of redistribution to ground of the circuit and the connection of the bottom plate of the additional capacitor C<sub>n-1A</sub> having the highest capacitance value in the array of redistribution to the ground change-over switch S<sub>Gn-1</sub> enforcing a complete discharge of the additional capacitor C<sub>n-1A</sub> having the highest capacitance value in the array of redistribution. Electric charge is accumulated simultaneously in the sampling capacitor C<sub>n</sub> and in the capacitor

- <sup>35</sup> C<sub>n-1</sub> having the highest capacitance value in the array of redistribution which is connected to the sampling capacitor C<sub>n</sub> in parallel. Both capacitors (C<sub>n</sub> and C<sub>n-1</sub>) are the only capacitors that are connected to the source of converted voltage U<sub>IN</sub> through the top plate change-over switches S<sub>Tn</sub>, S<sub>Tn-1</sub> and the input on-off switch S<sub>U</sub> and through the bottom plate change-over switches S<sub>Bn</sub>, S<sub>Bn-1</sub> and ground of the circuit. Fig. 9 presents the abovementioned state of the apparatus. [0049] After detecting the end of the trigger signal P<sub>x</sub> by the control module CM on the trigger input InS, the control

- <sup>40</sup> module CM by the use of the signal from the output controlling the change-over switches of plates A<sub>C</sub> causes additionally switching of the top plate change-over switches S<sub>Tn-1</sub>, S<sub>Tn-1A</sub> and switching of the bottom plate change-over switches S<sub>Bn-1</sub>, S<sub>Bn-1A</sub> and the connection of the top plate of the capacitor C<sub>n-1</sub> having the highest capacitance value in the array of redistribution to the source on-off switch S<sub>Hn-1</sub> and to the destination on-off switch S<sub>Ln-1</sub>, the connection of the top plate of the highest capacitance value in the array of redistributional capacitor C<sub>n-1A</sub> having the highest capacitance value in the input on-

- <sup>45</sup> off switch S<sub>U</sub>, the connection of the bottom plate of the capacitor C<sub>n-1</sub> having the highest capacitance value in the array of redistribution to the ground change-over switch S<sub>Gn</sub> and the connection of the bottom plate of the additional capacitor C<sub>n-1A</sub> having the highest capacitance value in the array of redistribution to ground of the circuit.

- [0050] As soon as the beginning of the next trigger signal  $P_{x+1}$  is detected by the control module CM on the trigger input InS, the electric charge is accumulated simultaneously in the additional sampling capacitor  $C_{nA}$  and in the additional capacitor  $C_{n-1A}$  having the highest capacitance value in the array of redistribution which is connected to the additional sampling capacitor  $C_{nA}$  in parallel. Both capacitors ( $C_{nA}$  and  $C_{n-1A}$ ) are the only capacitors that are connected to the source of converted voltage  $U_{IN}$  through the top plate change-over switches  $S_{TnA}$ ,  $S_{Tn-1A}$  and the input on-off switch  $S_{U}$  and through the bottom plate change-over switches  $S_{Bn-1A}$  and ground of the circuit.

- **[0051]** After detecting the end of the next trigger signal  $P_{x+1}$  by the control module CM on the trigger input InS, the control module CM by the use of the signal from the output controlling the change-over switches of plates  $A_C$  causes the switching of the top plate change-over switches  $S_{Tn-1}$ ,  $S_{Tn-1A}$  and switching of the bottom plate change-over switches  $S_{Bn-1}$ ,  $S_{Bn-1A}$  and the connection of the top plate of the capacitor  $C_{n-1}$  having the highest capacitance value in the array of redistribution to the input on-off switch  $S_U$ , the connection of the top plate of the additional capacitor  $C_{n-1A}$  having the

highest capacitance value in the array of redistribution to the source on-off switch  $S_{Hn-1}$  and to the destination on-off switch  $S_{Ln-1}$ , the connection of the bottom plate of the capacitor  $C_{n-1}$  having the highest capacitance value in the array of redistribution to ground of the circuit and the connection of the bottom plate of the additional capacitor  $C_{n-1A}$  to the ground change-over switch  $S_{Gn-1}$ .

- <sup>5</sup> **[0052]** According to the invention, another method for conversion of an instantaneous voltage value to the digital word realized in the exemplary apparatus differs from the previous methods in that as soon as the process of accumulated electric charge redistribution is terminated, the control module CM causes the electric charge, accumulated in the last of capacitors on which the reference voltage U<sub>L</sub> had not been reached during realization of the process of redistribution, to be conserved.

- <sup>10</sup> **[0053]** If the control module CM assigns the value zero to the bit  $b_0$  during the realization of the process of charge redistribution, the control module CM introducing the apparatus into the relaxation state by the use of the signal from the control output  $I_0$  causes the opening of the destination on-off switch  $S_{L0}$  and the disconnection of the top plate of the capacitor  $C_0$  having the lowest capacitance value in the array of redistribution from the destination rail L, the switching of the ground change-over switch  $S_{G0}$  and the connection of the bottom plate of the capacitor  $C_0$  having the lowest  $C_0$  and the connection of the source of auxiliary voltage L.

- <sup>15</sup> capacitance value in the array of redistribution to the source of auxiliary voltage U<sub>H</sub>. **[0054]** If the control module CM assigns the value one to the bit  $b_0$  during the realization of the process of redistribution, the control module CM introducing the apparatus into relaxation state by the use of the signal from the control output I<sub>i</sub> causes the opening the destination on-off switch S<sub>Li</sub> and the disconnection of the top plate of the source capacitor C<sub>i</sub> from the destination rail L, the switching of the ground change-over switch S<sub>Gi</sub> and the connection of the bottom plate

- <sup>20</sup> of the source capacitor C<sub>i</sub> to the source of auxiliary voltage U<sub>H</sub>.

#### References

| 25 | [0055]                                                                  |                                                                                          |

|----|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 20 | A                                                                       | array of redistribution                                                                  |

|    | An                                                                      | section of sampling capacitor                                                            |

|    | СМ                                                                      | control module                                                                           |

|    | K1                                                                      | the first comparator                                                                     |

| 30 | K2                                                                      | the second comparator                                                                    |

|    | J                                                                       | current source                                                                           |

|    | U <sub>H</sub>                                                          | source of auxiliary voltage                                                              |

|    | UL                                                                      | source of the reference voltage                                                          |

|    | U <sub>IN</sub>                                                         | converted voltage                                                                        |

| 35 | InS                                                                     | trigger input                                                                            |

|    | In1                                                                     | the first control input of the control module                                            |

|    | In2                                                                     | the second control input of the control module                                           |

|    | В                                                                       | digital output of the control module                                                     |

|    | OutR                                                                    | complete conversion output                                                               |

| 40 | Н                                                                       | source rail                                                                              |

|    | L                                                                       | destination rail                                                                         |

|    | C <sub>n</sub>                                                          | sampling capacitor                                                                       |

|    | C <sub>n-1</sub> , C <sub>n-2</sub> ,, C <sub>1</sub> , C <sub>0</sub>  | capacitors in the array of redistribution                                                |

|    | C <sub>n-1</sub>                                                        | capacitor having the highest capacitance value in the array of redistribution            |

| 45 | C <sub>0</sub>                                                          | capacitor having the lowest capacitance value in the array of redistribution             |

|    | C <sub>nA</sub>                                                         | additional sampling capacitor                                                            |

|    | C <sub>n-1A</sub>                                                       | additional capacitor having the highest capacitance value in the array of redistribution |

|    | C <sub>i</sub>                                                          | source capacitor                                                                         |

|    | C <sub>k</sub>                                                          | destination capacitor                                                                    |

| 50 | U <sub>n-1</sub> , U <sub>n-2</sub> ,, U <sub>1</sub> , U <sub>0</sub>  | voltages on the capacitors in the array of redistribution                                |

|    | U <sub>i</sub>                                                          | voltage on the source capacitor                                                          |

|    | U <sub>k</sub>                                                          | voltage on the destination capacitor                                                     |

|    | $b_{n-1}, b_{n-2},, b_i,, b_k,, b_1, b_0$                               | bits in the digital word                                                                 |

|    | S <sub>Hn</sub> , S <sub>Hn-1</sub> , S <sub>Hn-2</sub> ,,              | <b>4</b>                                                                                 |

| 55 | S <sub>Hi</sub> ,, S <sub>Hk</sub> ,, S <sub>H1</sub> , S <sub>H0</sub> | source on-off switches                                                                   |

|    | S <sub>Ln</sub> , S <sub>Ln-1</sub> , S <sub>Ln-2</sub> ,,              |                                                                                          |

|    | S <sub>Li</sub> ,, S <sub>Lk</sub> ,, S <sub>L1</sub> , S <sub>L0</sub> | destination on-off switches                                                              |

|    | S <sub>Gn</sub> , S <sub>Gn-1</sub> , S <sub>Gn-2</sub> ,,              |                                                                                          |

ground change-over switches top plate change-over switches bottom plate change-over switches destination rail on-off switch input on-off switch output controlling change-over switches of the plates output controlling the current source output controlling the input on-off switch trigger signal next trigger signal subsequent trigger signal control outputs

15

45

#### Claims